Sipeed Lichee Tang Specifications v1.0

- EG4S20

- 20K logic unit

- About 130KB SRAM

- Built-in 32bit width 64MBit SDRAM

- Many LVDS pins

- Built-in 12-bit 1MSPS ADC

Version 1.0 Sipeed Copyright © 2018 www.sipeed.com

www.sipeed.com

# **SiPEED** Sipeed Lichee Tang Specifications v1.0

| Functional Overview        |                                                                                                                                                                                                                                                                         |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core unit                  | Anlogic Technologies EG4S20                                                                                                                                                                                                                                             |

| Logical unit               | 20K (LUT4/LUT5 hybrid architecture)                                                                                                                                                                                                                                     |

| SRAM                       | About 130KB                                                                                                                                                                                                                                                             |

| SDRAM                      | Built-in 32bit bit width 64MBit                                                                                                                                                                                                                                         |

| Flash                      | FPGA configuration Flash, 8Mbit<br>User Flash, nor/nand optional                                                                                                                                                                                                        |

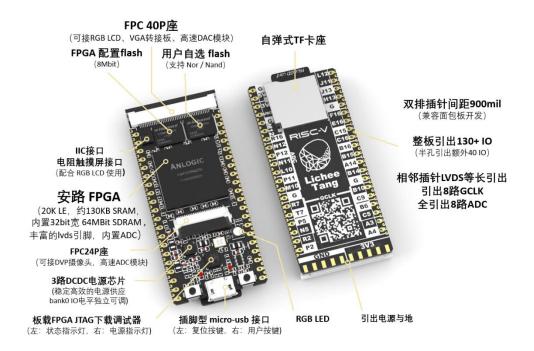

| interface                  | FPC40P socket, can be connected to RGB<br>LCD, VGA adapter board<br>FPC24P socket, can be connected to DVP<br>camera, high speed ADC module<br>Resistive touch screen controller for I2C<br>interface, used with RGB LCD                                                |

| Pin and lead               | The adjacent pins LVDS are drawn in the<br>same length, leading out 8 GCLKs, and all 8<br>ADCs are taken out.<br>Double row pin spacing 900mil, compatible<br>with breadboard development<br>Half hole leads to an extra 40 IO, and the<br>whole board leads to 130+ IO |

| Electrical characteristics | Micro USB 5V power supply; 2.54mm pin<br>3.3V~5V power supply; 1.27mm stamp hole<br>power supply<br>3-channel DCDC power supply chip, stable<br>and efficient power supply, independent<br>adjustment of Bank0 IO level                                                 |

| Download and debug         | Onboard FPGA JTAG Download Debugger<br>RV debugger can debug hummingbird core                                                                                                                                                                                           |

# Software function

Integrate, download, debug features with TD IDE IDE has a rich IP core Support hummingbird risc-v soft core https://github.com/Lichee-Pi/Tang\_E203\_Mini

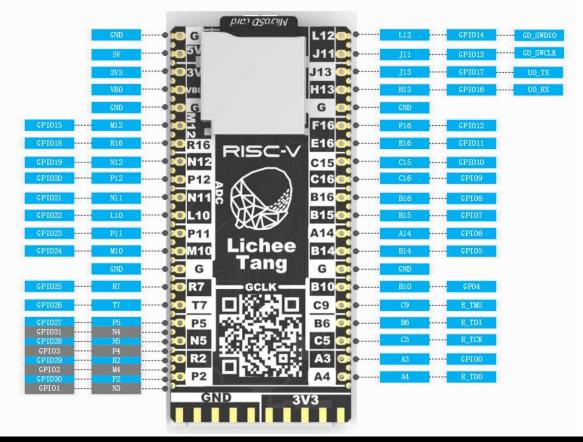

## Lichee Tang development board pin diagram

### Lichee Tang Development Board Resource Map

| Communicate communities and resources |                                |

|---------------------------------------|--------------------------------|

| Github                                | https://github.com/Lichee-Pi   |

| BBS                                   | http://bbs.lichee.pro/t/lichee |

| Wiki                                  | tang.lichee.pro                |

| E-mail                                | support@sipeed.com             |

| Size and weight          |             |

|--------------------------|-------------|

| Development board size   | 25.4x56.0mm |

| Development board weight | 6.2±0.1g    |

| Precautions                   |                                                                                                                    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| RV debugging                  | When using the RV debugger, if you need to use USB power, try to use a shorter USB cable.                          |

| Micro-USB                     | The USB interface can be used for power supply, and the interface is fragile. Please pay attention to the use.     |

| Download and debug            | On-board FPGA JTAG download debugger,<br>debugging hummingbird core requires other<br>debuggers, such as RV, JLink |

| Operating temperature         | -20~85°C                                                                                                           |

| Power consumption and current | No-load current is about 50mA                                                                                      |

#### Target application scenario:

- High-speed communication interface interconnection

- Learning, debugging, research of soft cores such as RISC-V

- Machine vision processing

- Parallel computing acceleration

#### **Disclaimer and copyright notice**

The information in this document, including the URL address for reference, is subject to change without notice.

The documentation is provided by Sipeed<sup>™</sup> without warranty of any kind, including any warranties of merchantability, and any proposal, specification or sample referred to elsewhere. This document is not intended to be a liability, including the use of information in this document to infringe any patent rights.

Copyrights © 2018 Sipeed Limited. All rights reserved.

Sipeed Technology